# vichfalt auc

MICROCOMPUTING FOR SMALL BUSINESS AND HOME VOLUME 2, ISSUE 12, NOVEMBER 1977

CANADA/MEXICO

INTERNATIONAL

\$1.75 \$2.00

\$3.00

## **How People and** Computers Map **Space**

Also: Computerized Fingerprint Search General Ledger-III A Byte of Music **Blockade Game**

## INTERFACE DESIGN WITH

by Alex Goldberger Signetics, Sunnyvale, California

Interfacing a microprocessor to peripheral devices is an important part of a total microcomputer system design. The characteristics of the interface depend to a large extent on total system requirements and other factors such as CPU loading and data speed. The use of interrupts and/or DMA structures also have an impact on the system input/output structure. The design of an I/O interface is not limited to hardware, and hardware/software trade-offs must be considered.

This article examines the use of the 2650's set of I/O instructions and the interface between the 2650 and I/O ports. Interrupt and DMA-controlled I/O are not discussed. A number of application examples for both serial and parallel I/O are given. Several types of input, output, and bidirectional interface devices are also examined.

#### **BASIC I/O STRUCTURE**

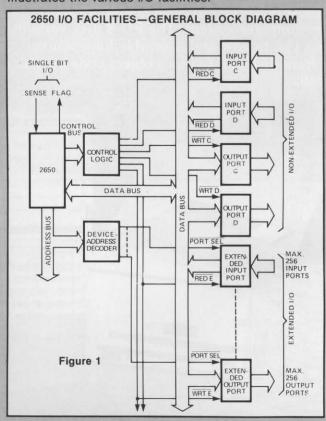

The 2650 is equipped with input and output facilities which can perform both single bit input/output and 8-bit parallel input/output.

The single bit input and output, called Sense (pin 1) and Flag (pin 40), are associated with the Program Status Word Upper (PSWU). The Flag output always reflects the value of bit 6 of the PSWU, while bit 7 of the PSWU always reflects the value of the Sense input signal. The Sense and Flag signals can be monitored and controlled with the PSW instructions.

Parallel I/O can be accomplished using the extended or non-extended read and write instructions. The extended and non-extended types are distinguished by the state of the  $E/\overline{NE}$  output of the microprocessor.

The non-extended I/O instructions are single-byte instructions which accomplish a 1-byte data transfer into or out of the 2650. They also control the state of the  $\overline{D/C}$  output, which can be used as a 1-bit device address in small systems.

The extended I/O instructions are 2-byte instructions. When executing extended I/O instructions, the second byte of the instruction is output on the lower 8 bits of the address bus (ADRO-ADR7). This information is normally used as an I/O device address to select 1 of up to 256 input or output devices, but may also be used to output control or status signals.

Parallel I/O operations may use any CPU register as the data source or destination. This offers significant flexibility in writing I/O software, because there is not a single accumulator register to create a "bottle-neck" in the data flow. The functional block diagram in Figure 1 illustrates the various I/O facilities.

#### I/O AS PART OF THE MEMORY ADDRESS SPACE

The 2650 user may choose to transfer data into or out of the processor using the memory control signals. The advantage of this technique is that the data can be read or written by the program with memory load and store instructions, and data may be directly operated upon with

## SIGNETICS 2650

logical and arithmetic instructions. The memory referencing instructions can take advantage of the flexible addressing modes provided by the system, such as indexing and indirect addressing. A possible disadvantage of this method is that it may be necessary to decode more address lines to determine the device address than with the other I/O facilities.

To make use of this technique, the designer must assign memory addresses to I/O devices and design the device interfaces to respond to the same signals as memory.

#### I/O INTERFACE SIGNALS

Table 1 summarizes the state of the 2650 I/O interface signals for the various methods of I/O which are available.

#### SENSE INPUT AND FLAG OUTPUT

One of the I/O capabilities of the 2650 is provided by the sense input and flag output. The sense and flag pins may be used for single-bit input or output of status or control information. They can also be used to implement a serial data communications channel. Two examples of this application are give below.

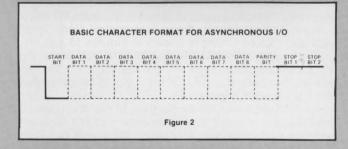

ASYNCHRONOUS SERIAL COMMUNICATIONS PORT: In applications where a serial type of terminal (like a teletype-writer) must be connected to the microcomputer systems, the sense pin and flag pin can be used to interface with the terminal. The basic character format for asynchronous serial I/O is shown in Figure 2.

A number of parameters of this character format, and the transmission speed, is different for various types of terminals. The variable parameters are: Baud rate (bits per second): 110, 150, 300, 600, 1200, 1300, 4800, and 9600 baud.

Number of bits per character: 5, 6, 7, or 8 bits. Parity mode: even, odd, and no parity.

Number of stop bits: 1 or 2.

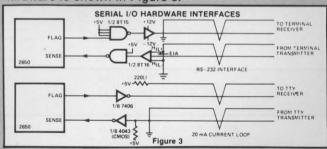

The control of the sense and flag pins for asynchronous serial I/O, with the appropriate parameters and baud rate, can be done completely with software. The hardware involved is limited to a simple line driver and receiver circuit which may be either and RS-232 interface or a 20mA current loop interface. The interface hardware is shown in Figure 3.

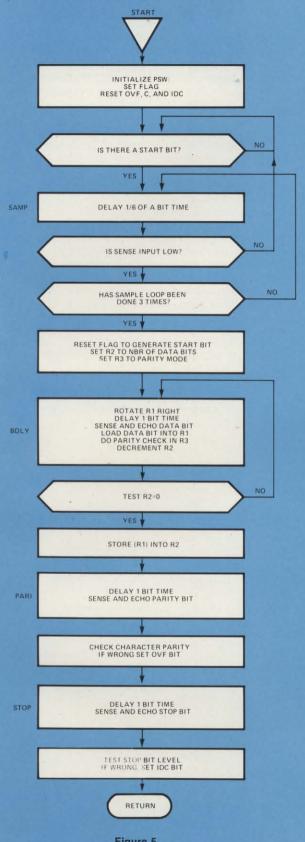

The software necessary to accomplish the serial I/O for a full-duplex line can be divided into 3 parts: 1) The start bit detection and verification. After each start bit detection, the start-bit level is verified for a low level at time intervals of 1/6 of 1-bit time. This prevents false start-bit recognition caused by line noise. 2) The sampling of the data bits at the mid-bit time, echoing the data bit to the flag output, and loading the data bit into a CPU register. 3) The input, echo and check of parity bit and stop bits.

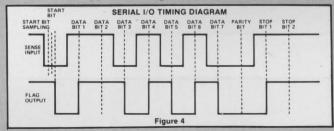

A timing diagram showing the start bit sampling and the bit echo appears in Figure 4.

| TYPE OF<br>I/O OPERATION | OPREQ | M/IO | R/W | ADRO-ADR7      | ADR13<br>(E/NE) | ADR14<br>(D/C) |

|--------------------------|-------|------|-----|----------------|-----------------|----------------|

| Sense (Input)            | X     | ×    | ×   | ×              | X               | X              |

| Flag (Output)            | X     | ×    | ×   | ×              | X               | X              |

| Extended Read            | Н     | L    | L   | Second Byte of | н               | ×              |

| Extended Write           | н     | L    | н   | Instruction    | Н               | X              |

| Non-Extended Read C      | H     | L    | L   | ×              | L               | L              |

| Non-Extended Read D      | н     | L    | L   | ×              | L               | Н              |

| Non-Extended Write C     | Н     | L    | н   | ×              | L               | - L            |

| Non-Extended Write D     | н     | L    | н   | ×              | L               | н              |

| Memory I/O Read          | н     | н    | L   | ADR0-ADR7      | ADR13           | ADR14          |

| Memory I/O Write         | Н     | Н    | н   | ADR0-ADR7      | ADR13           | ADR14          |

X = Don't Care

Table 1. I/O Interface Signal State

| BAUD<br>RATE | SAMPLE<br>DELAY<br>NUMBER AT<br>1.25MHz | BIT DELAY<br>NUMBER AT<br>1.25MHz | NUMBER OF<br>BDRR,R0<br>INSTRUCTIONS AT<br>1.25MHz | NUMBER OF<br>BDRR,R0<br>INSTRUCTIONS AT<br>1MHz |

|--------------|-----------------------------------------|-----------------------------------|----------------------------------------------------|-------------------------------------------------|

| 110          | D0                                      | E5                                | 5                                                  | . 4                                             |

| 300          | 4A                                      | C5                                | 2                                                  | 2                                               |

| 600          | 24                                      | DE                                | 1                                                  | 1                                               |

| 1200         | 11                                      | 6A                                | 1                                                  | 1                                               |

| 2400         | 07                                      | 30                                | 4                                                  | 1                                               |

Table II

|        |     | BUS | A       |                  |                  |  |

|--------|-----|-----|---------|------------------|------------------|--|

| RBA    | WBA | CLK | BUS A   |                  |                  |  |

| X      | 0   | 1   | WRITE   | (A → latci       | n)               |  |

| 0      | 1   | X   | READ (  | latch -A         | )                |  |

| 1      | 1.  | X   | HI-Z (T | HI-Z (Tri-state) |                  |  |

|        |     | BUS | В       |                  |                  |  |

| RBB    | WBB | WBA | CLK     | ME               | BUS B            |  |

| X      | ×   | X   | X       | 1                | HI-Z             |  |

| 1      | 0   | X   | X       | 0                | HI-Z             |  |

| X      | 1   | 0   | ×       | 0                | HI-Z             |  |

| X<br>0 | 0   | X   | X       | 0                | READ (latch→B)   |  |

| X      | 1   | 1   | 1       | 0                | WRITE (B > latch |  |

Table III. 8T31 Control Functions

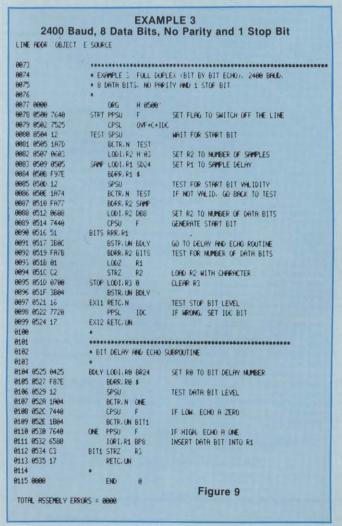

Three examples of the serial I/O routine with different speed and parameters are presented in Figures 5 through 9. The bit and sample delay number (hexadecimal) in the definition listing (Figure 6) are for a CPU clock frequency of 1MHz. The hexadecimal delay numbers for a frequency of 1.25MHz are given in Table 11. This table also lists the number of BDRR,RO instructions that are necessary in the "bit delay and echo subroutine" to count cycles for the appropriate baud rate.

The serial I/O routine uses four CPU registers (1 band and RO) and affects seven of the Program Status Word bits; namely, Sense, Flag, Overflow, Carry Interdigit Carry, and the two Condition Code Bits. The program also uses one level of the return address stack.

A parity error will set the Overflow bit, and a framing error (wrong stop bit level) will set the Interdigit Carry bit. At the end of the routine, the input character is stored in register R2.

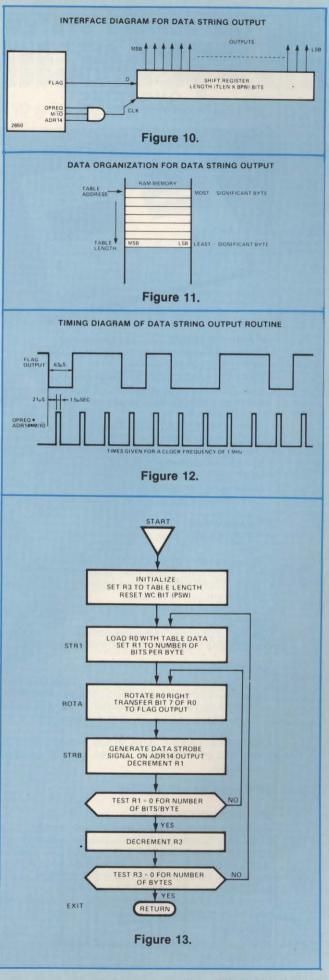

DATA SPRING OUTPUT: A typical application for the flag output is a data string output. The advantage for this output method is that it can provide a large number of output bits with little address or control logic decoding. For example, this method can be used to output data for an array of numeric displays, single bit indicators, or column drivers of a parallel numeric printer. An example of the hardware required to implement this type of output channel is given in Figure 10.

Here, the Address 14 output is used as a data strobe signal. However, the data strobe signal could also be built up by decoding more address bits so that the system memory size would not be limited to 16K bytes as in this example.

A listing of the program required is given in Figure 14. The data is assumed to be located in the system's RAM as illustrated in Figure 11.

The least-significant bit of the least-significant byte will be output first. The table length (TLEN) and the number of bits per byte (BPW) can be adapted as necessary by software modifications. The data strobe pulse on output ADR14 is generated by doing the dummy instruction STRA, RO to address H'4000'.

#### PARALLEL INPUT/OUTPUT

The 2650 instruction set contains the following six input/output instructions:

|               |                | NO. BYTES |

|---------------|----------------|-----------|

| WRTC, RX      | Write Control  | 1         |

| REDC, RX      | Read Control   | 1         |

| WRTD, RX      | Write Data     | 1         |

| REDD, RX      | Read Data      | 1         |

| WRTE, RX DEVA | Write Extended | 2         |

| REDE, RX DEVA | Read Extended  | 2         |

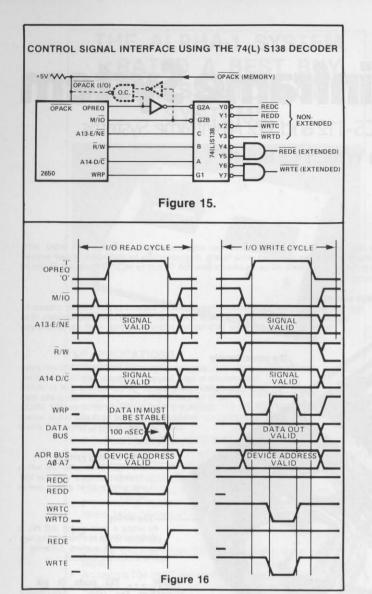

The control signals generated by each I/O instruction simplify the interface circuitry required to generate I/O selection and timing signals. A low-cost control signal interface with related timing is shown in Figures 15 and 16.

When using standard TTL and 8T series I/O ports, the I/O operations can be done without slowing down the system. In this case the OPACK input could be controlled directly for all I/O operations.

NON-EXTENDED I/O: The single-byte I/O instructions of the 2650 are referred to as non-extended I/O. In small systems with only two 8-bit input ports and two 8-bit output ports, this I/O facility requires a minimum of hardware interfacing between the CPU and I/O ports. The signals WRTC, WRTD, REDC, and REDD generated by the control logic decoder in Figure 15 can be used

#### FLOWCHART OF THE SERIAL I/O ROUTINE

Figure 5

#### SERIAL I/O PARAMETER DEFINITIONS THIN ASSEMBLER VER 1 8 PROE 8881 LINE ADOR OBJECT E SOURCE \* PD768891 0002 0003 \*\*\*\* PROGRAMMABLE SERIAL 1/0 ROUTINE \*\*\*\* 0005 0006 . WITH THIS PROGRAM THE SENSE AND FLAG INPUT/OUTPUT OF 0007 . THE 2650 ARE USED TO INTERFACE WITH TERMINALS 9998 . SUCH AS TTY, CRT TERMINALS, ETC. VIA THE BIT SERIAL 9999 9919 \* RSYNCHRONOUS LINE DISCIPLINE 9911 9912 \* ALL CHARACTER AND LINE PARAMETERS ON BE MODIFIED. . SIMPLY IN THE SOFTWARE THESE PARAMETERS ARE BAUD 9813 9814 9815 9816 9817 9818 9819 9829 9821 9822 9821 9822 9823 9824 9824 9824 \* RATE. NUMBER OF DATA BITS: PARITY MODE AND STOP BITS \* THE PROGRAM HAS BEEN SET UP FOR A FULL DUPLEX LINE . BUT CAN EASILY BE MODIFIED TO HALF DUPLEX MODE \* DEFINITIONS OF SYMBOLS RB EQU 8 PROCESSOR REGISTERS R1 EGAL EQU 0025 0003 EQU 9825 9883 9826 9858 9827 9848 9828 9828 9829 9884 9838 9881 EQU H188 PSU SENSE FOU H'48 FLAG 10C EUU H'29 INTERDIGIT CARRY OVE EQU H: 84 OVERELOW. C EQU CHRRY/BORRON H'91 0031 0002 EWU BRANCH CONDITION NEGATIVE 8832 8881 EQU UNCONDITIONEL \* SOFTWARE DEFINITIONS OF BRUD RATE, CHARACTER FORMAT, PARITY. \* PARITY MODE, ETC. \* MIMBER OF DATA BITS DB8 E0U H'08 CHARACTER HAS 8 DATA BITS. H 88 DB7 EQU H'07 CHARACTER HAS 7 DATA BITS PP-7 EQU H'48 DB6 EOU H 86 CHARACTER HAS 6 DATA BITS BP6 EQU H 28 H 85 805 EQU CHARACTER HAS 5 DATA BITS 9948 9965 9949 9919 9958 9951 9952 9953 9968 BP5 EQU H'10 . BIT DELAYS AT 1 MHZ CLOCK FREQUENCY BR01 EQU H E8 BIT DELAY AT 110 BAUD 8854 8869 8855 8868 BROS EQU BIT DELAY AT 300 BAUD H: 69 BROG EQU H:50 BIT DELRY AT 688 BAUD 9855 9969 9656 9653 9657 9825 9658 9669 9661 9865 9662 9838 9663 9816 9864 9886 9865 9865 BR12 EQU H 53" BIT DELAY AT 1280 BAUD BR24 EQU H 25 BIT DELAY AT 2400 BAUG \* START BIT SAMPLE DELAWS AT 1 MHZ CLOCKERFOLENCY 5001 E00 SAMPLE DELAY AT 110 BALD 5003 EQU H 3A SAMPLE DELRY AT 380 BAUD SDEG EQU H 10 SAMPLE DELAY AT 680 BAUD S012 EQU H' BC SAMPLE DELRY BT 1299 BRUD S024 EQU H 95 SAMPLE DELAY AT 2400 BAUD 9966 9967 9968 . PRINTY HODE EVEN PREITY 8869 8888 EP 9979 9989 OP EOU H 88 OCO PHRITY 9971 Figure 6

directly as output port clock pulses and input port enable signals, respectively.

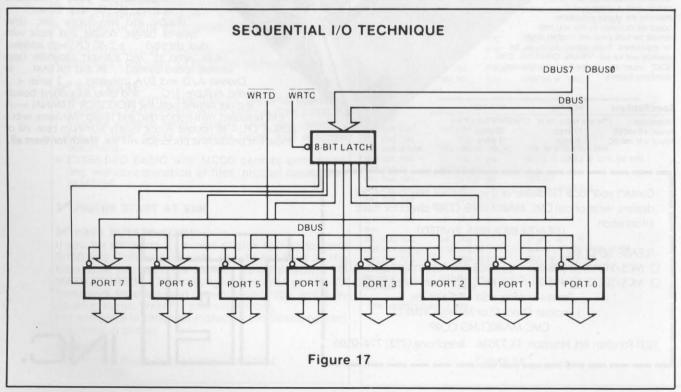

SEQUENTIAL I/O WITH NON-EXTENDED I/O INSTRUCTIONS: In systems where a larger number of devices must be serviced in sequence, the use of a simple 8-bit output port can offer considerable savings in software. Normally the devices could be serviced with extended I/O instructions. However, since the device address is the second byte in this type of instruction, a series of data fetch and I/O instructions would be required to service the devices in sequence.

With an 8-bit output port functioning as a device address register, the device address can be modified under software control. In this way, a simple program loop can serve up to eight I/O ports by rotating a single '1' through a CPU register that is output as a device address. This I/O addressing technique may also be used advantageously in systems where I/O operation requests are detected by software polling. A functional block diagram of this technique is shown in Figure 17.

EXTENDED I/O: There are two extended I/O instructions in the 2650 instruction set. In these 2-byte instructions, the first byte specifies the operation code and the data source or destination register in the CPU. The second byte provides an 8-bit device address code that is output on the eight least-significant bits of the address bus, ADR0 through ADR7.

SERIAL I/O ASSEMBLY LISTING-EXAMPLE 1 110 Baud, 7 Data Bits, Even Parity and 1 Stop Bit LINE ADDR OBJECT E SOURCE 9973 9974 9975 9976 • EXAMPLE 1 FULL DUPLEX (BIT BY BIT ECHO), 118 BRUD. • 7 DATA BITS, EVEN PARITY AND 1 STOP BIT 9977 9999 H'0500 8878 8589 7648 STRT PPSH SET FLAG TO SHITCH OFF THE LINE 9879 8582 7525 9889 8584 12 CPSL OVF+C+100 TEST SPSU WALT FOR START BIT 8881 8585 1A70 BCTR. N TEST 8882 9597 9683 L001, R2 H-03 SET R2 TO NUMBER OF SAMPLES 8883 8589 85A5 SAMP LODI. R1 SUB1 SET R1 TO SAMPLE DELAY 8984 8588 F97E 8985 8580 12 BDAR, R1 \$ SPSU TEST FOR START BIT WALIDITY 0086 850E 1A74 BCTR. N TEST IF NOT VALID, GO BACK TO TEST 9887 8519 FA77 BORR, R2 SAMP 8888 8512 8788 LODI, R3 EP SET R3 TO EVEN PARITY MODE 8889 8514 8687 L001. R2 DB7 SET R2 TO NUMBER OF DATA BITS 8898 8516 7448 CPSII GENERATE START BUT 0091 0518 51 BITS RRR, R1 8892 8519 3812 BSTR. UN BOLY GO TO DELAY AND ECHO ROUTINE BOAR, R2 BITS 0093 051B FA7B TEST FOR NUMBER OF DATA BITS LODZ R1 STRZ R2 8894 851D 81 R1 8895 851E C2 LORD R2 WITH CHRRHCTER 9996 951F 3B90 PART BSTR. UN BOLY 9897 9521 9982 9898 9523 7764 BCFR, N STOP IF WRONG PRICITY, SET OVE PPSL OWF 8899 8525 8788 STOP LOGI, R3 0 CLEAR R3 0100 0527 3804 BSTR. UN BOLY 0101 0529 16 EXI1 RETC. N TEST STOP BIT LEVEL TINE 9192 8528 7729 PPGI IF WRONG, SET ICC BIT EXIZ RETC. UN 9193 8520 17 9194 0105 . BIT DELRY FIND ECHO SUBROUTINE 0107 8188 8520 84E8 BOLY LODT, R9 BR91 SET RO TO BIT DELAY NUMBER 0109 052F F87E BORR, RE \$ 0110 0531 F87E PLAR. FR S BURR, FIR \$ 0111 0533 F87E BORR, RB \$ 9112 9535 F87E 0113 0537 12 SPSU TEST DATABIT LEVEL 9114 9538 1R94 BCTR, N ONE IF LOW. ECHO A ZERO 0115 053A 7440 BETR. UN BIT1 9116 953C 1B94 0117 053E 7640 PPQI IF HIGH, ECHO A ONE 1001, R1 BP7 INSERT DATABIT INTO RE 0118 0540 6540 BIT1 EORZ R3 0119 0542 23 STRZ R3 DO PHRITY CHECK 0120 0543 C3 RETC. UN 0121 0544 17 0122 FND B Figure 7 TOTAL ASSEMBLY ERRORS = 8888

The control signal decoding diagram (Figure 15) can be simplified for systems using only extended I/O, as shown in Figure 18. The timing diagram of Figure 16 also applies to this decoding technique.

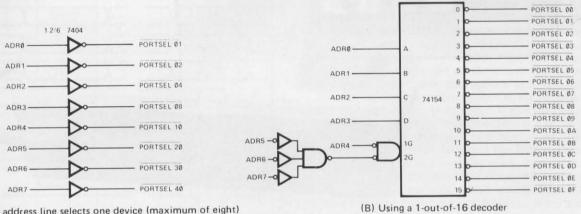

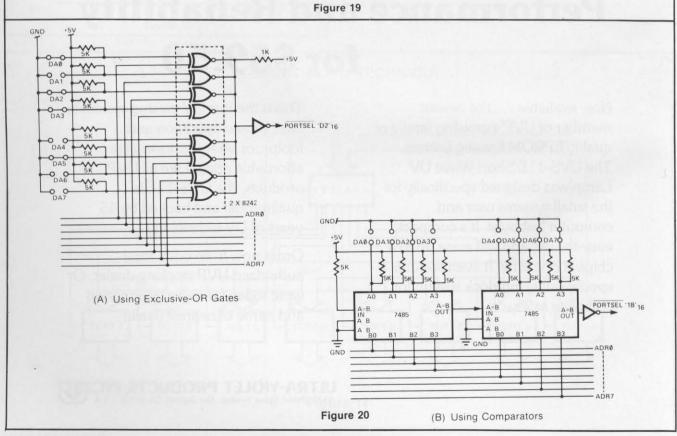

DEVICE ADDRESS DECODING SCHEMES: For extended I/O it is necessary to decode the address lines ADR0 through ADR7 in order to generate appropriate port selection signals. The choice of an address decoding scheme depends on factors such as total I/O requirements, the type of I/O ports used, and the total system configuration.

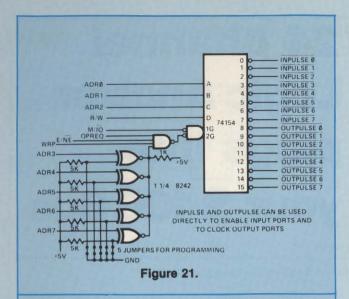

In principle, there are two basic methods of device address decoding. One method is the use of hardwired logic in which the device address is fixed; the other is a hardware programmable method in which the device addresses are individually set with jumpers or switches. Some examples of these methods are given in Figures 19 and 20.

In many applications a combination of these two methods is used. In addition, the control logic can be implemented as an integral part of the device address decoding. An example is shown in Figure 21.

MEMORY MAPPED 1/0: In memory mapped 1/0, the 1/0 devices are treated as memory locations. An advantage of this technique is that all memory referencing instruction types (store, load, arithmetic, logical, etc.) can be used directly for 1/0 data. Device address decoding is

| 600 Bar                      | ud. 7 Data E                     | EXAMI<br>Bits. Od | PLE 2<br>Id Parity and 2 Stop Bits                                                                                                            |

|------------------------------|----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| LINE ADDR DEJE               |                                  |                   | a , and 2 otop 200                                                                                                                            |

| 8873                         | *******                          | ********          | ***************************************                                                                                                       |

| 9974                         |                                  |                   | LEX (BIT BY BIT ECHO). 688 BAUG.                                                                                                              |

| 9875                         |                                  | TS, 000 PA        | RITY AND 2 STOP BITS                                                                                                                          |

| 9976                         | 100                              |                   |                                                                                                                                               |

| 9877 9999                    | ORG                              | H: 0500           | SET FLAG TO SWITCH OFF THE LINE                                                                                                               |

| 0078 0500 7640               | STRT PPSU                        | F                 | SET FLAG TO SMITCH OFF THE LINE<br>C<br>HAIT FOR START BIT<br>SET R2 TO NUMBER OF SAMPLES                                                     |

| 9879 8582 7525               | CPSL                             | OVF+C+ID          | C.                                                                                                                                            |

| 9888 8584 12                 | TEST SPSU                        | 200               | MHIT FOR STHRT BIT                                                                                                                            |

| 9981 9585 1H/U               | BCTR) N                          | I TEST            | CET DO TO MARKE OF COMPLEY                                                                                                                    |

| 9862 8587 8683               | COMP LOCAL D                     | 2 H 03            | SET RI TO SHAPLE DELRY                                                                                                                        |

| 9884 9588 F97E               | DUDG D                           | 1 3000            | SET KI TO SHIPLE DELIN                                                                                                                        |

| 9995 9590 12                 | BORR, R                          | * *               | TEST ENG STORT BIT UG INTO                                                                                                                    |

| 8886 858E 1874               | PETE N                           | TEST              | IF NOT WALLD, ON PACK TO TEST                                                                                                                 |

| 9987 9518 FR77               | BORR, R                          | 2 SEEF            | in the factor we take to the                                                                                                                  |

| 9988 9512 9788               | L001, R                          | 3 OP              | TEST FOR START BIT VALIDITY  IF NOT VALID, GO BACK TO TEST  SET R3 TO GOO PARTTY MODE  SET R2 TO NUMBER OF DATA BITS  GENERATE START BIT      |

| 9989 8514 9687               | L001, R                          | 2 DB7             | SET R2 TO NUMBER OF DATA BITS                                                                                                                 |

| 8898 8516 7448               | CPSU                             | F                 | SET R2 TO NUMBER OF DATA BITS GENERATE START BIT  GO TO DELAY AND ECHO ROUTINE TEST FOR NUMBERS OF TOTA BITS                                  |

| 0091 0518 51                 | BITS RRP. R1                     |                   |                                                                                                                                               |

| 0092 0519 3B1A               | BSTR, U                          | N BULY            | GO TO DELRY AND ECHO ROUTINE                                                                                                                  |

| 8893 851B FA7B               |                                  |                   | TEST FOR NUMBER OF DATA BITS                                                                                                                  |

| 9894 851D 81                 |                                  | Ri                |                                                                                                                                               |

| 8895 851E C2                 | CTET                             | F-7               | LORD R2 WITH CHRRICTER                                                                                                                        |

| 8896 851F 3814               | PHRI BSTR. U                     | N BOLY            |                                                                                                                                               |

| 9897 8521 9882               | BCFR, N                          | 5101              |                                                                                                                                               |

| 9898 9523 7794               | PHIRI BSTR. U<br>BCFR. N<br>PPSL | CVF               | IF MRONG PHRITY, SET OVE                                                                                                                      |

| 0099 0525 0700               | ST01 L001, R                     | 3 0               | CLEMP RS                                                                                                                                      |

| 0100 0527 3B0C               | STO1 LOO1, R<br>BSTR. U          | N BOLY            |                                                                                                                                               |

| 0101 0529 1A02               | BCTR, N                          | \$102             | TEST STOP BIT LEVEL                                                                                                                           |

| 0102 0526 7720               | PPSL                             | TOC               | IF MFONG, SET IDC BIT                                                                                                                         |

| 0103 0520 0700               | 5102 L001, R                     | 3.0               | CLEAR R3                                                                                                                                      |

| 8184 802F 3884               | BSTR, U                          | N BOLY            |                                                                                                                                               |

| 01 05 0531 16                | EXII REIC. N                     | 100               | TEST STOP BIT 2 LEVEL                                                                                                                         |

| 0100 0032 7720               | FOLO DETC II                     | 100               | IF MACING, SET TOC BIT                                                                                                                        |

| 0107 0034 17                 | EXIZ KEIL, U                     |                   |                                                                                                                                               |

| 0100                         |                                  |                   |                                                                                                                                               |

| 9119                         | . DIT NELDY                      | OND COUNTY        | CHECKATTAE                                                                                                                                    |

| 9111                         | * DIT DELIN                      | THE EURO          | IF MRONG PHRITY, SET OVE CLEAR RS  TEST STOP BIT LEVEL IF MRONG, SET IDC BIT CLEAR RS  TEST STOP BIT 2 LEVEL IF MRONG, SET IDC BIT SUBROUTINE |

| 9112 9535 94BB               | BOLY LODT, R                     | B ERBS            | SET RR TO RET DELAY MINRED                                                                                                                    |

| 9113 9537 F87F               | BORP, P                          | 8 \$              | SET RO TO BIT DELAY NUMBER                                                                                                                    |

| 9114 9539 12                 | SPSU                             |                   | TEST DATA BIT LEVEL                                                                                                                           |

| 9115 953A 1A84               |                                  | ONE               | and the second                                                                                                                                |

| 9116 953C 7449               | CPCII                            | c                 | IF LON, ECHO R ZERO                                                                                                                           |

| 9117 953E 1B94               | BCTR. U                          | N BITI            |                                                                                                                                               |

| 9118 9549 7649               | ONE PPSU                         | F                 | IF HIGHL ECHO R ONE                                                                                                                           |

| 9119 9542 6548               | IORL R                           | 1 BP7             | INSERT DATA BIT INTO RE                                                                                                                       |

| 9129 9544 23                 | RITH FORZ                        | R3                |                                                                                                                                               |

| 8121 8545 C3<br>8122 8546 17 | STRZ                             | N.S               | DO PHRITY CHECK                                                                                                                               |

| 9122 9546 17                 | PETC. U                          | N                 |                                                                                                                                               |

| 9123                         |                                  |                   |                                                                                                                                               |

| 9124 9888                    | END                              | 9                 | Figure 8                                                                                                                                      |

|                              |                                  |                   |                                                                                                                                               |

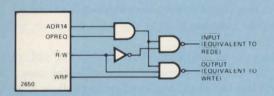

not necessarily more complex than for normal extended I/O, since all I/O addresses could be located in a specific address block. Of course, this technique can only be used in systems which do not use the full memory address space for programs. A diagram of the I/O control logic, using the ADR14 output to discriminate between memory and I/O operations, is given in Figure 22. The device address decoding methods described earlier can also be applied to memory mapped I/O.

#### SINGLE POINT CONTROL

In many applications, the capability to set, clear, or test a single output point selected from a large number of output points is required. Designs of this type can be implemented using the 2650 I/O instructions. When used as described below, the WRTE, WRTC, and WRTD instructions become "set/clear single-bit" instructions, while the REDE instruction becomes a "test single-bit" instruction.

SINGLE BIT OUTPUT-DIRECT ADDRESS: The write extended instruction can be used to select and set or clear a single output bit. The two bytes of the instruction can be interpreted as follows:

# THE ALPHA-1 SYSTEM ✓RATED A BEST BUY IN MASS STORAGE SYSTEMS

#### **APPLICATIONS**

BUSINESS applications include mailing lists, payroll, billing, and inventory.

CASSETTE BACKUP for disk-based Systems not only provides large amounts of storage at low cost, but also provides for convenient storage of historical records.

DEVELOPMENT SYSTEM features include a powerful operating System with an Editor, Assembler, and Debugger, plus a variety of System utilities which speed development.

OEM applications include P.O.S. data capture, word processing systems, audio-visual presentation systems, telephone call transfer systems.

#### **HARDWARE**

- Stores greater than 500K bytes per side of a C-60 tape.

- · Access a file in 17 seconds average on a C-60 tape.

- · Load 8K of data in less than 11 seconds (6250 baud).

- 100% interchangeability of cassettes with no adjustments required or allowed.

- Compatible with all popular S-100 Bus Microcomputers.

- Audio track under computer control.

- Eliminates the need for ROM/PROM monitors.

#### **✓** SOFTWARE

- MCOS, a powerful stand-alone cassette operating system, is operationally much simpler than a D.O.S., handles variable length named files, will update a file in place, packs or copies tapes with a single command.

- EXTENDED BASIC with MCOS permits array handling and concatenation of files, plus all capabilities of MCOS

#### PRICES START AT \$240

#### FREE BUYERS GUIDE

If you are shopping for a tape or disk system for your S-100 Bus Computer System, you do not have all the facts until you have the MECA "BUYERS GUIDE TO MASS STORAGE." This 10 page guide book provides a framework for evaluating cassette, cartridge, and disk-based systems. Write for your copy today.

For complete information including the Dealer nearest you, write or phone:

#### meca

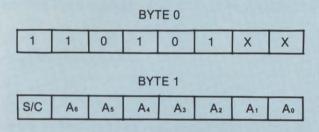

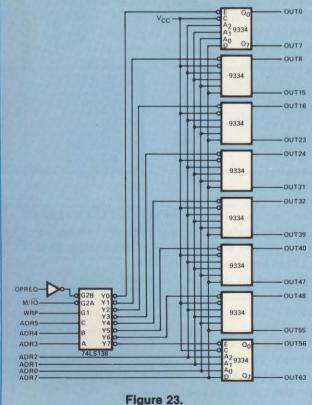

7026 O.W.S. Road, Yucca Valley, CA 92284 (714) 365-7686 Ao through Ao of the second byte specify the output selected. The S/C bit specifies whether the bit is set or cleared. A typical hardware configuration controlling 64 points is shown in Figure 23. Here, the control line decoding and partial address decoding is done by the 74LS138, which selects one of the eight 9334s. One of the eight latches in the selected 9334 is enabled by ADRO, ADR1, and ADR2 and is either cleared or set, as determined by the value of ADR7.

The XX field in the first byte selects one of the four available registers and outputs in its contents on the data bus. Since this information is not used in this application, the value of XX is not important. However, it could be used to output an 8-bit control or status word in conjunction with the set/clear operation.

SINGLE BIT OUTPUT-INDIRECT ADDRESS: If the address of the output to be set or cleared must be determined at program run time, the WRTD and WRTC instructions can be used. The address of the output bit is first loaded into one of the 2650 registers. A WRTD, Rx instruction is

#### ASSEMBLY LISTING OF DATA STRING OUTPUT ROUTINE

THE DOOR DETECT & SOURCE

| LINE ROOR | OBJECT | E SOUR | E           |           |       |            |                            |

|-----------|--------|--------|-------------|-----------|-------|------------|----------------------------|

| 0001      |        | * P0   | 768894      |           |       |            |                            |

| 9992      |        | ****   | ******      | ******    | ****  | *******    | *******************        |

| 9993      |        |        |             |           |       |            |                            |

| 9994      |        |        |             | **** DATE | STRI  | NG OUTPUT  | ROUTINE ****               |

| 9995      |        |        |             |           |       |            |                            |

| 9996      |        | * TH   | IS PROGRE   | M TRANSFE | RS TH | E CONTENT  | S OF A MEMORY TABLE IN BIT |

| 9997      |        | * BI   | SERIAL      | FORM TO 1 | HE FL | AG OUTPUT  | OF THE 2658                |

| 9998      |        |        |             |           |       |            |                            |

| 9999      |        | * TH   | TABLE I     | ENGTH AND | THE   | NUMBER OF  | BITS ARE SOFTWARE PROGRAM  |

| 9919      |        |        |             |           |       |            |                            |

| 0011      |        | * A I  | MTA STR     | DE OUTPUT | 15 G  | ENERATED   | ON THE ADDRESS 14 DUTPUT   |

| 9012      |        |        |             |           |       |            |                            |

| 0013      |        | ****   | ******      | ********  | ****  | *******    | *******                    |

| 0014      |        |        |             |           |       |            |                            |

| 0015      |        | * DE   | INITION     | OF SYMBO  | LS    |            |                            |

| 0016      |        |        |             |           |       |            | and the second             |

| 9917 9999 |        | RØ     | EQU         | Û         | PROC  | ESSOR REG  | ISTERS                     |

| 9918 9991 |        | R1     | EQU         | 1         |       |            |                            |

| 0019 0002 |        | R2     | EQU         | 2         |       |            |                            |

| 9829 9993 |        | R3     | EQU         | 3         |       |            |                            |

| 9821 9989 |        | 5      | EOU         | H:80      | PSU   | SENSE      |                            |

| 0022 0040 |        | F      | EQU         | H'49'     |       | FLAG       |                            |

| 9923 9999 |        | MC     | EQU         | H'88'     | PSL   | 1=HITH     | 0=WITHOUT CARRY            |

| 9824 9992 |        | N      | EQU         | 2         | BEHN  | CH COND    | NEGRTIVE                   |

| 0025 0003 |        | UN     | EQU         | 3         |       |            | UNCONDITIONAL              |

| 0026      |        |        | (17.75.7s)  |           |       |            |                            |

| 9827 9987 |        | TLEN   | EQU         | H'87      | THEL  | E LENGTH   |                            |

| 9828 9998 |        | BPW    |             |           | NUMB  | ER OF BIT  | S PER BYTE                 |

| 8629      |        |        |             |           |       |            |                            |

| 8838 8888 |        |        | ORG         | H'0680'   |       |            |                            |

| 9931 9699 |        | TREL   |             |           | 1,008 | TION OF T  | ABLE .                     |

| 8832      |        |        | -           |           |       |            |                            |

| 9933      |        | ****   | ******      | *******   | ***** | *******    | ******                     |

| 9834      |        |        |             |           |       |            |                            |

| 8835 8687 |        |        | OPG         | H 9589    |       |            |                            |

| 9836 9588 |        | STRT   | L001, R3    |           |       |            |                            |

| 9937 9592 |        | 2161   | CPSL        | MC        |       |            |                            |

| 9938 9594 |        | CTD4   | A1000 Table | TABL, RO  | 1.09  | r. pa WITH | TABLE DATA                 |

| 9839 9587 |        | 31112  | LOOL RI     |           |       |            | MBER OF BITS PER BYTE      |

| 9848 9589 |        | POTO   | RRR PB      |           | -     | N. 10 100  |                            |

| 9941 958F |        | KUIN   |             | ONE       | TEC   | TBIT       |                            |

| 8842 8580 |        | 2000   |             | F         | 0.70  | ZERO, RES  | ET ELOG                    |

|           |        | ZEKU   | BCTR, UN    |           | 11    | EERO, KES  | El Tulo                    |

| 9943 956E | 1504   |        | BL IK, UN   | SIKD      |       |            |                            |

| 9844      |        | *      | 5070 W      |           |       |            |                            |

| 9845 9516 | 4000   | HUK    | DATA H      | 40,00     |       |            |                            |

| 0046      |        |        | 00011       |           | 10    | OUE CET    | EL OC                      |

| 9947 9512 |        | 0.000  |             | F         |       | ONE. SET   |                            |

| 8648 8514 |        | STRE   | STRAL RE    |           | -     |            | ROBE SIGNAL ON R14         |

| 0049 0517 |        |        |             | ROTA      |       |            | BER OF BITS                |

| 9959 9515 |        | E1/    | BORR, R3    |           | TES   | I FUK NU   | BER OF BYTES               |

| 9951 951E |        | FXII   | RETC, UN    |           |       |            |                            |

| 9952 9996 | 5      |        | END 0       |           |       |            |                            |

TOTAL ASSEMBLY ERRORS = 0000

Figure 14

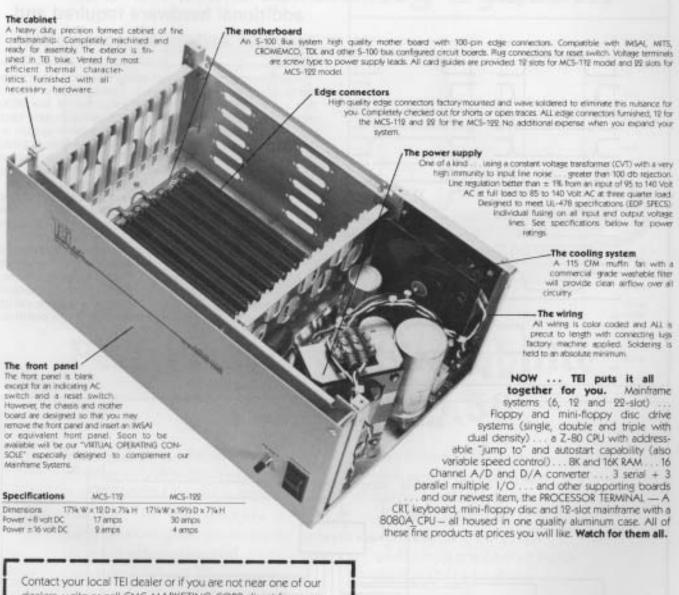

# Computer Mainframe System

First in the TEI family . . . The MCS-112 and 122 Mainframe Systems.

#### "The Base on Which to Build"

NC.

then issued if the bit is to be set, and a WRTC, Rx instruction is issued if the bit is to be cleared. The bit select is output on the data bus, and the D/C output carries the *set/clear* information. The hardware implementation can be the same as shown in Figure 23, except that ADR0-ADR5 are replaced by DBUS0-DBUS5, and ADR7 is replaced by D/C.

# The 8T31 can be used to implement a flag register without the use of a memory byte in RAM. No additional hardware required and memory savings are considerable.

SINGLE BIT INPUT: One way of doing single bit input uses the techniques described earlier. The address of the bit that is to be tested is loaded into one of the 2650 registers and output to an 8-bit latch using an extended or non-extended write instruction. The latch output is decoded to select the desired bit, which is then applied to the Sense input pin. The 2650 Program Status Word instructions can then be used to test the state of the Sense input and to take appropriate program action.

The technique described above must be used if "indirect" bit addressing is required. If this is not a requirement, a more efficient implementation can be accomplished using the extended read instruction. This technique makes use of the fact that the 2650 automatically tests the contents of a register every time it is used as the destination of an operation. Thus, when the read extended operation reads data from an input port, the condition code bits in the program status word are set to reflect whether the new register contents is positive, negative, or zero.

# New UVS-11E EPROM Erasing System

# Performance and Reliability for \$59.50

Now available . . . the newest member of UVP's growing family of quality EPROM Erasing Lamps. The UVS-11E Short Wave UV Lamp was designed specifically for the small systems user and computer hobbyist. It's compact, easy-to-use, and will erase up to 4 chips at one time. It even features a special safety interlock system for complete safety.

This is the first UV erasing system to offer simple operation and foolproof safety features at an affordable price. Like all UVP products, the UVS-11E is quality-built and backed by 45 years of UV technology.

Order now from your local authorized UVP stocking dealer. Or write today for more information and name of nearest dealer.

ULTRA-VIOLET PRODUCTS, INC. 0100 Walnut Grove Avenue, San Gabriel, CA 91776 U.S.A.

#### SIMPLIFIED CONTROL LOGIC WHEN USING EXTENDED I/O ONLY 2/6 74LS04 M/IO G2A G2B 1/2 741 520 M/IO OPREQ REDE Y2 E/NE E/NE С 74(L)S138 Y3 Y4 Y5 Y6 R/W В R/W REDE 74LS30 OPREO WRTE Y7 WRP WRE 2650 (A) Using 1-of-8 Decoder (B) Using Logic Gates Figure 18

#### SOME POSSIBLE TECHNIQUES FOR DEVICE ADDRESS DECODING

(A) Each address line selects one device (maximum of eight)

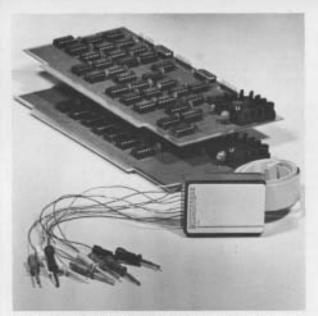

24 Channel LOGIC ANALYZER, complete with 2 cards and 3 sets of probes (only one set shown).

#### Features

- 24 channels with 256 samples each.

- Display of disassembled program flow.

- Dual mode operation external mode analyses any external logic system. Internal mode monitors users data and address bus.

- Selectable trigger point anywhere in the 256 samples.

- 0-16 bit trigger word format or external qualifier.

- 10MHz sample rate (50ns min. pulse width)

- Synchronous clock sample with coincident or delayed clock mode.

- User defined reference memory.

- Displays and system control through keyboard entry.

- TTL Logic level compatible (15 pf and 15 µa typical input loading).

- Includes annotated source listing.

Display of disassembled program flow.

# Databyte, Inc.

P.O. Box 14 7433 Hubbard Avenue Middleton, Wisconsin 53562 Tel: (608) 831-7666

**NOVEMBER 1977**

# 24 channel Logic Analzer plugs into your S-100 Bus

#### The DATALYZER

The Databyte Logic Analyzer (DATALYZER) is a convenient, flexible, high quality device. Efficient engineering has allowed a combination of features previously available in only the most expensive units.

Designed to plug easily into your S-100 Bus, the DATALYZER is a complete system — for only \$495. Display of disassembled program flow is a standard feature, not an extra. And the low price includes 30 logic probes, so you can hook up immediately, without additional expense.

The DATALYZER is available in kit form (\$495), and as a fully assembled device on two PCB's (\$595). Four-week delivery, a substantial warranty, and the Databyte, Inc. commitment to service make the DATALYZER a worthwhile investment. Begin debugging by sending the coupon now.

Displays in Hex

| DR: 28    | U DES           | (818)        | 205   |  |

|-----------|-----------------|--------------|-------|--|

| - KK - 88 | MI DOM          | -            | man.  |  |

|           | WC 4888         | BOTES!       | W     |  |

| 720       | <b>54</b> (8)80 | DER RICH     | 88    |  |

|           | AL RESE         | 1001190      |       |  |

|           | MI THE RE       | -            | -     |  |

|           | 2 5 5 5 5 5     | 100          | AE C  |  |

| -         |                 |              | -     |  |

| _         |                 |              | -     |  |

|           | DIA MARCH       | -            | -     |  |

| _         | MI DESI         | -            |       |  |

| 100       | MICHEUM T       | 10000        | 100   |  |

| 181       | MF BORD         | 200          | 100   |  |

| 18.5      | E 200           | <b>HARRY</b> | IDA . |  |

| 18.5      | 100 3000        | 100.00       | 100   |  |

| 2.5       | -               |              | -     |  |

Displays in Binary

| Please send me the  Kit – (manual i Assembled and Operators' manu Delivery of all item Name | included) \$495.00<br>Tested (manual inc<br>al only \$7.50 | (Wis, res, add 4%)<br>cluded) \$595,00 |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|

| Address                                                                                     |                                                            |                                        |

| City                                                                                        | State                                                      | Zip                                    |

| Telephone                                                                                   | TEADACT                                                    |                                        |

| Payment Enclosed:                                                                           | Check                                                      | Money Order                            |

| ☐ BankAmericard                                                                             |                                                            |                                        |

| Number                                                                                      |                                                            |                                        |

| Signature                                                                                   |                                                            |                                        |

I/O CONTROL SIGNAL GENERATION FOR MEMORY MAPPED I/O

Figure 22.

### SIXTY-FOUR SINGLE BIT OUTPUTS USING THE 9334

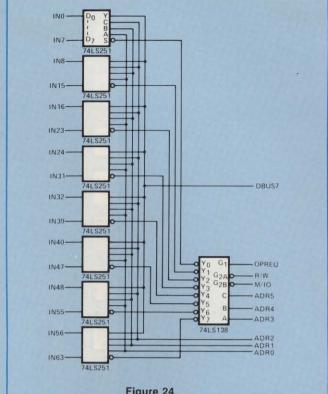

For the single bit input application, the second byte of the RETE. Rx instruction contains the address of the input bit to be tested. This data is applied to a bank of data selectors to select the addressed bit, which is then applied to the most-significant bit of the data bus, DBUS7. Since this is interpreted as the sign bit, the condition code bits in PSL will be set to reflect whether the bit being tested is a one or zero. A conditional branch instruction can then be used to affect the desired program action. A hardware implementation for 64 inputs is shown in Figure 24. Note that an address latch is not required for this method.

#### INPUT PORT DEVICES

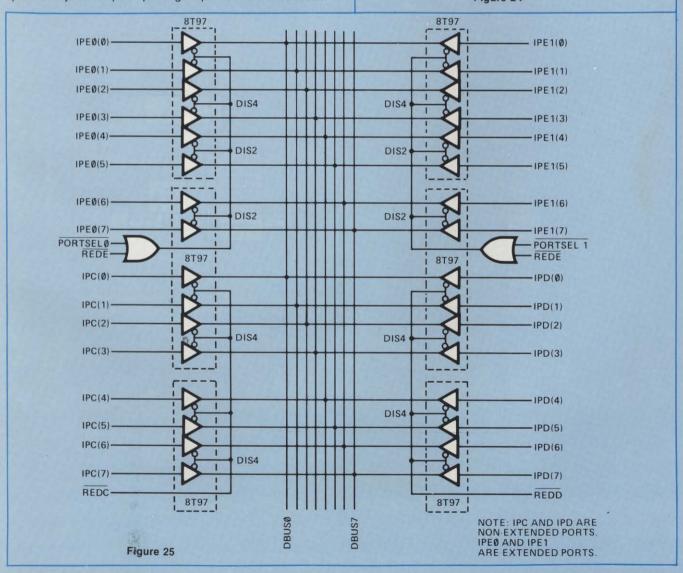

GATED INPUT PORTS: The simplest form of an input port is the tri-state gate. Figure 25 illustrates the use of the 8T97 high-speed HEX tri-state buffer for gated input ports. The 8T97 is non-inverting, and the tri-state control signals enable the buffers in groups of four and groups of two, so that 8-bit ports can be implemented efficiently.

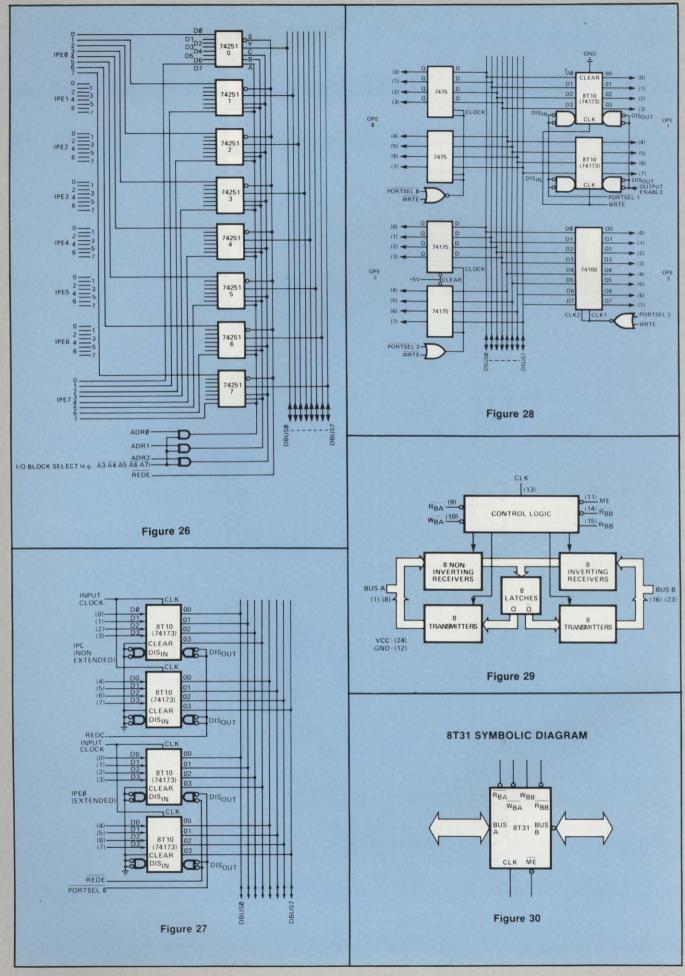

An effective circuit for systems using 8-gated input ports is the 74251 8-to-1 multiplexer, which has tri-state outputs that can interface directly with the data bus. The advantage of this circuit is that no external address decoding logic is needed. A configuration using gated input ports with the 74251 multiplexer is illustrated in Figure 26.

In addition to these two configurations, many other input port configurations are possible using standard

TTL or Signetics 8T series logic circuits.

LATCHING INPUT PORTS: Latching input ports may be required to store data from an external device, which is available only momentarily, before the actual input operation to the microprocessor takes place. This type of input port can be realized by connecting TTL-latch or D-type flip-flop circuits, such as the 7475, 74100, or 74175, to the inputs of a gated input port. As illustrated in Figure 27, by using the Signetics 8T10 Quad D-type flip-flop with tri-state outputs, an 8-bit latching input port can be implemented with only two packages. The 8T10 is functionally identical to the 74173.

#### **OUTPUT PORT DEVICES**

Output ports can be configured with a variety of standard TTL and 8T series flip-flops and registers. Typical circuits include:

9334 Addressable 8-bit latch

7475 Quadruple latch

74100 8-bit latch

74175 Quadruple D-type flip-flop

8T10 Quadruple D-type flip-flop with tri-state

ouputs

The 7475 and 74175 both have true and complement outputs. One special feature of the 8T10 is that the outputs may be disabled (placed in a high-impedance output mode) by the device that is connected to this output port. A logic diagram using these circuits for output ports appears in Figure 28.

The 9334 is useful in systems requiring a large number of latched outputs, since a portion of the decoding can be done using the on-chip 3-input decoder. A typical application of this was shown in Figure 23. It is also an efficient circuit for implementing eight 8-bit output ports.

#### I/O CONFIGURATIONS USING THE 8T31 **BIDIRECTIONAL PORT**

The 8T31 is an 8-bit bidirectional I/O port consisting of eight clocked latches with two bidirectional I/O buses, each of which has its own control logic. Each bus (A and B) has a read and a write control input, and there is a

master enable input for bus B only. The outputs of the latches follow the inputs when the clock is high, and latching will occur when the clock returns low.

The 8T31 is also equipped with a "power-on clear" circuit. If the clock input is held low until the power supply reaches 3.5V, the latches will be cleared. There is a logic inversion between bus A and bus B. As a result, when the 8T31 is cleared, bus A will have all logic "1" outputs and bus B all logic "0" outputs.

The control functions of the 8T31 are listed in Table 111. A functional block diagram and a symbolic diagram of the 8T31 are illustrated in Figures 29 and 30, respectively. As shown in Table 111, each bus can operate independently except for the care of writing from both bus A and B. In this case writing from bus A will override any attempt to write from bus B.

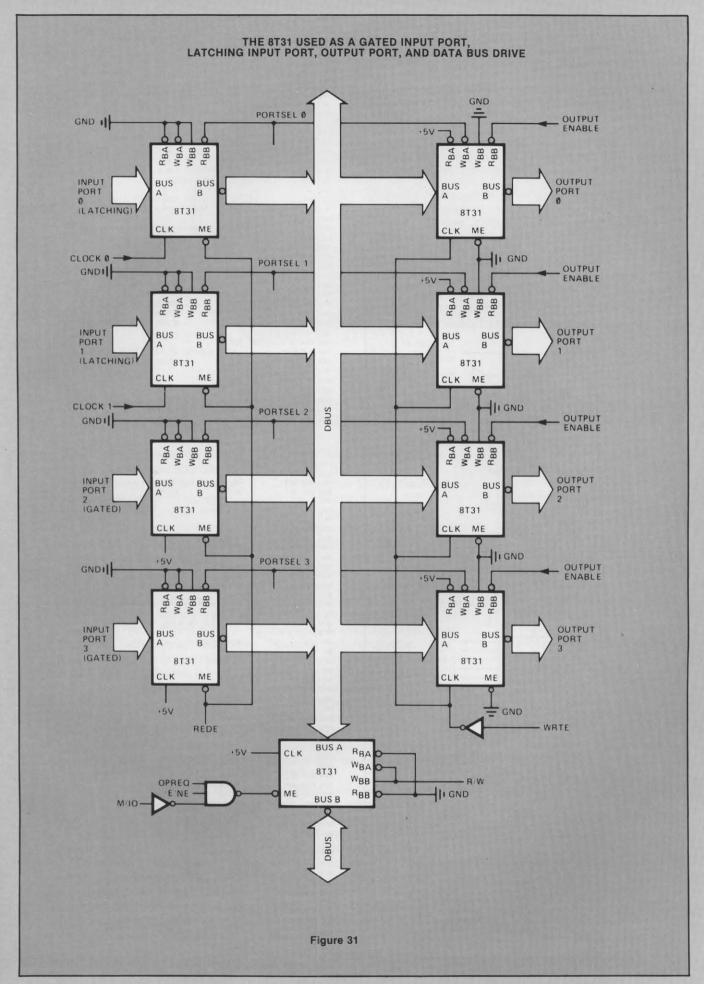

The control functions of the 8T31 allow it to be used in various microcomputer input/output applications. In the I/O system diagram of Figure 31, the 8T31 is used to implement gated input ports, latching input ports, output ports, and a bidirectional data bus driver. All I/O ports can be controlled directly with the device select and REDE and WRTE lines coming from device decoders and I/O control logic.

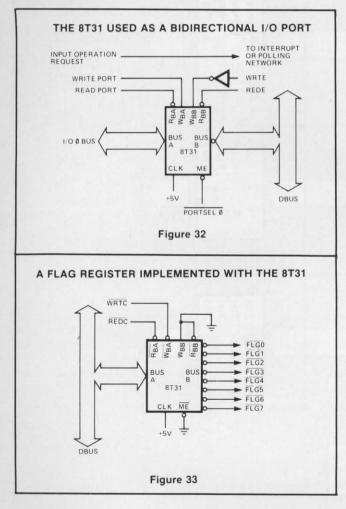

In applications where interfacing is necessary with peripheral devices that need data transfers in two directions, like digital cassettes and data link communication circuits, the 8T31 can be used as a bidirectional I/O port. In this application, the I/O operation should be requested by interrupt or polling to prevent simultaneous

Figure 24

write operations from peripheral and CPU. The bidirectional I/O port concept is illustrated in Figure 32.

In many industrial applications, such as process control, single bit inputs and outputs are used to monitor switches and detectors or to drive relays and lamps. A possible solution for such an 8-bit flag register would be an 8-bit output port and a memory byte reserved as a flag register in the system's RAM. The setting, resetting, or testing of individual bits with this method of implementing a flag register requires many bytes of program memory. The output port and the memory location reserved as a flag register image must be updated after each bit operation.

The 8T31 can be used to implement a flag register without the use of a memory byte in the system's RAM. No additional hardware is required, and the saving in program memory bytes for flag operations is considerable. A logic diagram of this application is given in Figure 33. Listings of basic software to set, reset, and test individual flags for both positive and negative true outputs are given in Figures 34 and 35.

| THIN PESSEN | BLER YER | 1.0 PRGE                                       | 9991     | 16    |

|-------------|----------|------------------------------------------------|----------|-------|

| LINE ROOR   | OBJECT   | E SOURCE                                       |          |       |

| 9991        |          | * P0768898                                     |          |       |

| 8882        |          | ***************************************        | *******  | 11    |

| 9993        |          |                                                |          |       |

| 9994        |          | * **** FLAG MANIPULATION EXAMPLES ****         |          |       |

| 9995        |          |                                                |          |       |

| 9996 .      |          | . THIS LISTING GIVES SOME EXPMPLES HON TO SET, | RESET    |       |

| 9997        |          | . AND TEST INDIVIDUAL BITS OF AN EXTERNAL FLAG | REGISTER |       |

| 9998        |          | . BUILT WITH THE 8T31 BIDIRECTIONAL I/O PORT   |          |       |

| 9999        |          | . INSTRUCTIONS ARE GIVEN FOR BOTH ACTIVE "HIGH | ' AND    |       |

| 9919        |          | * ACTIVE 'LON' OUTPUTS                         |          |       |

| 9911        |          |                                                |          |       |

| 0012        |          | ***************************************        | ******   | int a |

| 0013        |          | •                                              |          |       |

|             |          |                                                |          |       |

```

* DEFINITIONS OF SYMBOLS

8915

9916 9999

89

PROCESSOR REGISTERS

FOU

9917 9991

R1

EQU

9918 9962

EQU

0019 0003

R3

FOIL

9828 9888

EQU

BRANCH COND

ZER0

9821 9883

UN

FOL

UNCONDITIONAL

9822 9999

FL.

EQU

ALL BITS ARE 1

9927

8824 8881

FLGO EQU

FLAG 8

0025 0002

FLG1 EQU

H'82

FLAG 1

8826 8884

FLG2 FOU

H'84

FLAG 2

9927 B999

FLG3 FOU

H'RR

FLAG 3

0028 0010

FLG4 EQU

H'18

FLAG 4

0029 0020

FLG5 EQU

H'28

8838 8848

FLG6 EQU

H'48

FLAG 6

9931 9989

FLG7 FQU

H'89

FLAG 7

0032

DUMMY ADDRESS OF ROUTINE 'ONE

0033 0600

ONE EQU

9934 9659

ONES EQU

H'06501

DUMMY ADDRESS OF ROUTINE 'ONES'

8875

8936

0037

0038

**INSTRUCTIONS FOR ACTIVE 'LOW' OUTPUTS**

8839

0040 0000

H'8588

8842

SET FLAG(S)

9943

8844 8588 38

SNEG REDC, RO

LOAD FLAG REGISTER IN RO

0045 0501 6404

IORI, RO FLG2

SET FLAG 2

RESTORE FLAG REGISTER

8846 8583 BB

MPTC. PR

8847

8848 8584 38

SNES REDC. RO

9849 9585 6468

10R1, R8 FLGS+FLG6 SET FLAGS 5 AND 6

9959 9597 B9

MRTC, RO

RESTORE

9951

0052

RESET FLAG(S)

0053

0054 0508 30

DMEG DETYC DO

8855 8589 44FB

AND I. RO H'FF'-FLG2 RESET FLAG 2

9856 9586 BB

HRTC. RB

RESTORE

Figure 34

THIN ASSEMBLED VER 1 A

PAGE 8882

LINE ADDR OBJECT E SOURCE

9958 959C 39

RNFS REDC. RO

8859 8580 449F

AND 1, RO H'FF'-FLGS-FLG6 RESET FLAGS 5 AND 6

8068 858F B8

MRTC, RO

RESTORE

0061

TEST FLAG(S)

8860

0063

0064 0510 30

0065 0511 F404

TMI. RO FLG2

TEST FLAG 2

0066 0513 100600

BCTR. RL DNE

BRONCH IF ONE

9968 9516 39

9969 9517 F468

THES REDC. RO

THI. RO FLGS+FLG6 TEST FLAGS 5 AND 6

0070 0519 100650

BRANCH IF BOTH ARE ONE

BCTR, AL ONES

9972

0073

9974

**INSTRUCTIONS FOR ACTIVE "HIGH" OUTPUTS**

9975

9976 951C

OPG.

H 8558

9977

9978

SET FLAG(S)

0079

9889 8559 39

9881 8551 44FB

SPEG REDC. RA

AND1. R9 H'FF'-FLG2 SET FLAG 2

9982 9553 B9

MRTC, RO

RESTORE

0083

8884 8554 78

SPES REDULER

9985 9555 44ED

ANDI. RO H'FF'-FLG1-FLG4 SET FLAGS 1 AND 4

9986 9557 B9

MRTC, RO

9987

RESET FLAG(S)

9988

0089

0090 0558 30

RPFG REDC. RO

0091 0559 6404

IORI, RØ FLG2

RESET FLAG 2

9992 955B B9

MRTC, RO

RESTORE

0093

9994 955C 38

RPFS REDC, RO

0095 0550 6412

IORI. RO FLG1+FLG4 SET FLAGS 1 AND 4

0096 055F BB

MRTC, RO

RESTORE

9997

TEST FLAG(S)

0098

0099

9199 9569 39

TPFG REDC, RO

0101 0561 F404

THI. RO FLG2

TEST FLAG 2

BRANCH IF ONE

0102 0563 900600

BCFR, AL ONE

0103

0104 0566 30

TPFS REDC, RO

8185 8567 F412

8186 8569 908658

THI. RB FLG1+FLG4 TEST FLAGS 1 AND 4

BCFR. AL ONES

BRANCH IF BOTH ARE ONE

9197

END

8188 8888

TOTAL ASSEMBLY EXRORS = 8886

```